Unlike the traditional system-on-chip (SoC) design process, which has fully qualified verification methods embodied in the form of process design kits (PDKs), chip design companies and assembly houses have no integrated circuit (IC) package co-design sign-off verification process to help ensure that an IC package will meet manufacturability and performance requirements. Package die are often produced using multiple processes and multiple foundries, which raises the level of complexity, but also increases the need for a process that can ensure these disparate products can be manufactured within a single package. I discussed the need for PDKs for interposer and 3D designs in a previous blog. I’m happy to say now that there has been some advancement on this front.

Chip Package Verification Challenges

The new class of packages coming into the market enhances the interactions between the layers, so there is no clear separation between the traditional die and package, necessitating a unified co-design flow. A chip-scale package (CSP) is one type of IC package. To qualify as chip scale, the package must have an area no greater than 1.2 times that of the die and it must be a single-die, direct surface mountable package.1

The wafer-level package (WLP) is a type of CSP that enables the IC to be attached face down to the printed circuit board (PCB) using conventional surface mount technology (SMT) assembly methods. The chip’s pads connect directly to the PCB pads through individual solder balls. The die may be mounted on an interposer upon which pads or balls are formed, like with flip chip ball grid array (BGA) packaging, or the pads may be etched or printed directly onto the silicon wafer, resulting in a package very close to the size of the silicon die. WLP technology differs from other ball grid array, leaded, and laminate-based CSPs in that no bond wires or interposer connections are required. The main advantages of the WLP are a small package size, a minimized IC-to-PCB inductance, and a shortened manufacturing cycle time.

However, the challenges of verifying these packages are numerous. For example, a 28nm chip may contain as much as 75% non-28nm content. Ensuring that everything conforms to the 28nm requirements is a safe approach, but a time-consuming one, which may lead to missed schedules and late deliveries. Just using multiple die in a package increases failure risk and unforeseen integration issues. As previously mentioned, chips in a package often come from different foundries, and were verified using different processes, making package failures hard to identify and fix. We need better characterization of package processes and requirements to avoid ad hoc solutions from designers and assembly houses.

Of course, similar issues exist even for a single die in a package. There is no formal verification process to ensure the connectivity even from a single die to the BGA balls (and essentially, the “outside world” of the package) is correct.

The industry is, however, making a heroic effort to ameliorate the situation. Assembly houses have been packaging for years, and have a variety of tools to help them. However, they write their own rules for the assembly, with no reference sign-off deck. In addition, assembly houses rarely hold their customers to a hard and fast rule deck like the foundry does.

Assembly Design Kits

The purpose of an “assembly design kit” is similar to that of the process design kit—ensure manufacturability and performance using standardized rules that ensure consistency across a process. An assembly design kit could reduce the risk of package failure, increase packaging business, and increase the use of 2.5/3D packages.

An assembly design kit should include both a physical verification and extraction sign-off solution, and maybe thermal and/or stress sign-off solutions. All of these should be independent of any specific design tool used to create the assembly, and they must be validated by the package assembly/outsourced assembly and test (OSAT) company.

But a design kit is much more than just the sign-off requirements. Designers need validated technology files for the design creation tools, just like we have for place and route and custom design tools in the IC space today. And then there are the design-for-test strategies. If an assembled package fails, how do you trace back to the root cause of that failure?

I’ve been involved in a project to prove the feasibility of a physical verification solution to enable packaging rules that are independent of any specific package design or die process. We collaborated with a chip design company and an assembly house to develop a prototype assembly design kit for 2.5/3D IC packages. The goal was to create a method for presenting a fully-stacked system that included both DRC and LVS performed on each fabric independently AND at the interfacing level (die-to-die, die-to-package, etc.). The assembly design kit needed to handle multiple IC and package layout design formats:

- IC layout formats: LEF/DEF, OpenAccess, GDSII/OASIS (gridded design, geometries with vertices)

- Package layout formats: MCM, SiP, ODB++, Gerber (gridless design, shapes with arcs)

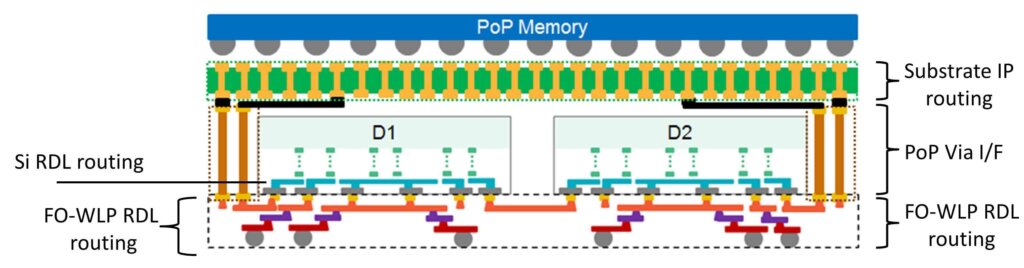

It also needed to provide support for assembly and stress rule checking. The design we used for feasibility testing was a side-by-side package using an embedded Fan-Out Wafer-Level Packaging (FOWLP) technology to support multi-die integration (Figure 1).

Defining Requirements and Responsibilities

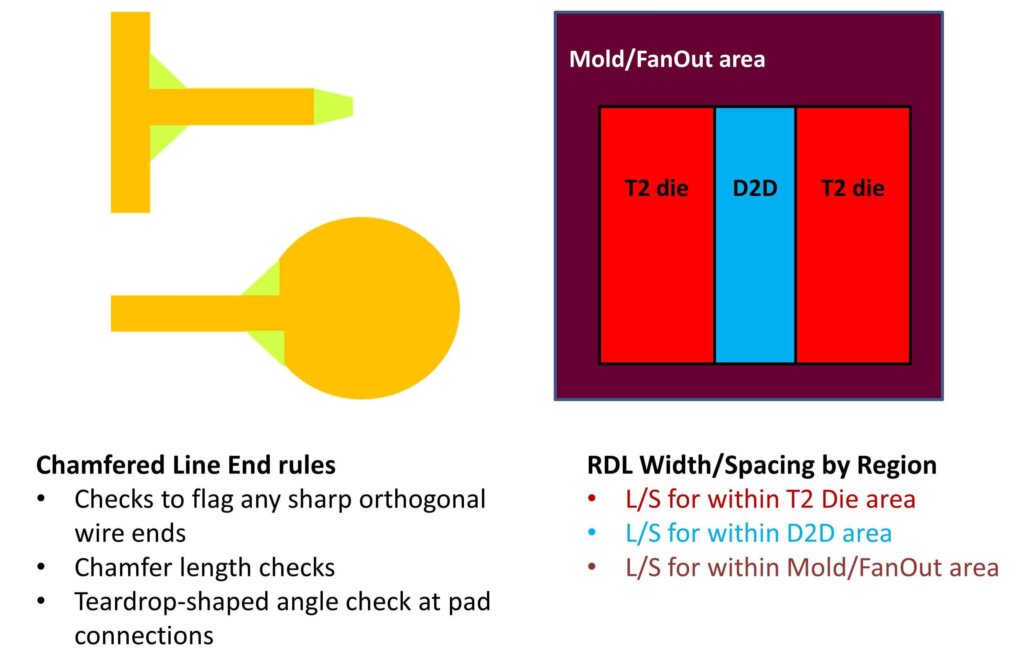

The chip design house wrote the design rules that defined what the assembly should look like, including how to DRC and LVS comparisons on packages. Design rules had to be created that addressed package-specific requirements, including specifics such as size and distance of package wires. Figure 2 shows some typical design rule checks that might be included in an assembly design package.

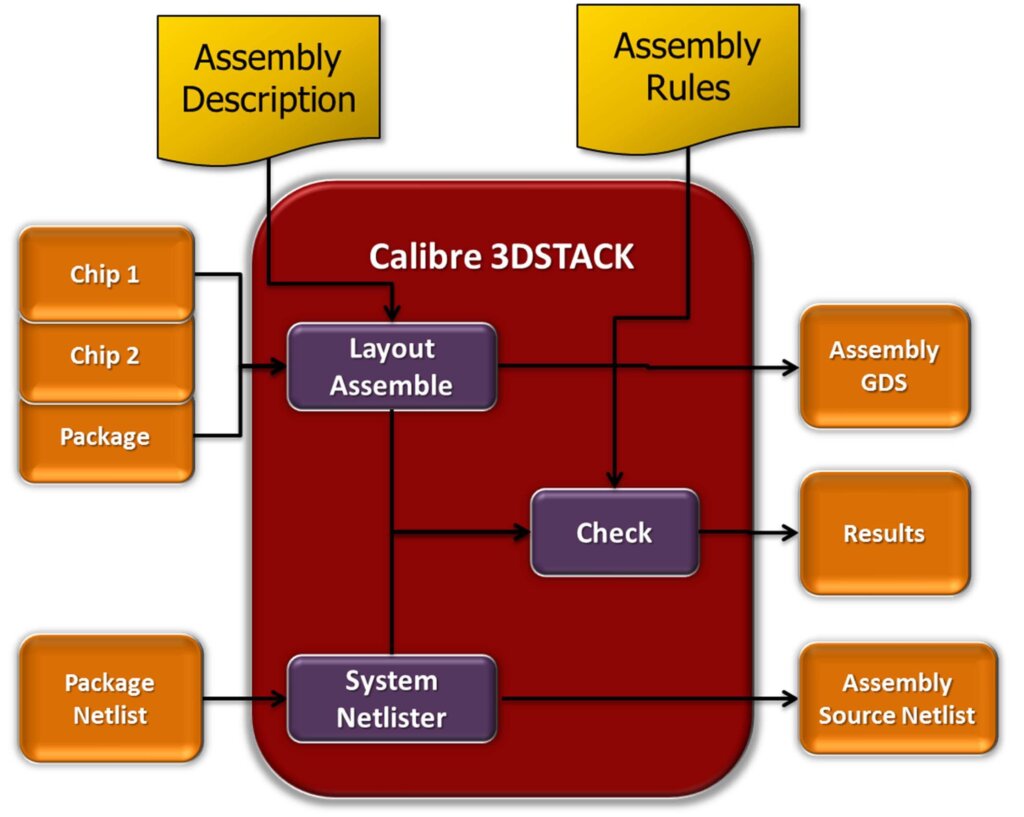

The assembly house wrote rules for the TYPES of elements and configurations permitted in the package. This includes die-to-die edge, die-to-package edge, die-to-package alignment, corner rules, etc. Mentor’s role was to enhance the syntax in the Calibre® 3DSTACK tool to bring the two rule sets together and provide rule checking capabilities (Figure 3).

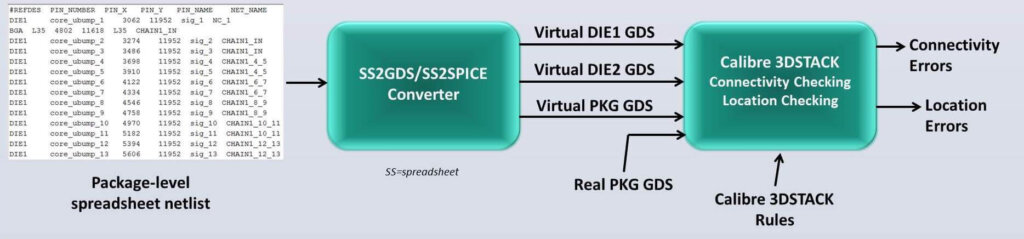

For LVS, the first challenge was the absence of a traditional source netlist for a package. In its place, we determined that the de facto industry substitute, a spreadsheet format that has been used for years, was satisfactory.

The assembly design kit LVS process is shown in Figure 5. We used virtual die in the LVS process to enable package layouts to be tested prior to assembly. We also had to develop a method for checking connectivity of standalone package design (no devices), as well as improve the existing solution for capturing netlist (connectivity intention) for a fully-stacked system (IC + package).

The project went quite well, and we delivered the results at DAC 2015. Using Calibre 3DSTACK, the assembly house was able to create a rule file for their FOWLP process. This rule file can be used by any designer targeting this package technology at this assembly house, regardless of what processes the dies are, or how many dies are in the package. The rule file checks the manufacturing constraints of the package RDL and the die-to-die constraints, and verifies the connectivity through the package from die-to-die and die-to-BGA. It is entirely independent of any specific design tool used to generate the package.

The assembly design kit provides a standardized process both chip design companies and assembly houses can use to ensure the manufacturability and performance of IC packages. Using an assembly design kit can reduce risk of package failure, while also reducing turnaround time for both the component providers and assembly houses. By implementing a repeatable, proven process, all participants can improve both their first-time success rate and overall product quality.

References

1.IPC standard J-STD-012, Implementation of Flip Chip and Chip Scale Technology. http://www.ipc.org/toc/j-std-012.pdf

Authors

John Ferguson is the Director of Marketing for Calibre DRC Applications at Mentor Graphics in Wilsonville, Oregon, and has extensive experience in the area of physical design verification. He holds a BS degree in Physics from McGill University, an MS in Applied Physics from the University of Massachusetts, and a PhD in Electrical Engineering from the Oregon Graduate Institute of Science and Technology. John may be reached at john_ferguson@mentor.com.

John Ferguson is the Director of Marketing for Calibre DRC Applications at Mentor Graphics in Wilsonville, Oregon, and has extensive experience in the area of physical design verification. He holds a BS degree in Physics from McGill University, an MS in Applied Physics from the University of Massachusetts, and a PhD in Electrical Engineering from the Oregon Graduate Institute of Science and Technology. John may be reached at john_ferguson@mentor.com.

Tarek Ramadan is a Technical Marketing Engineer for Calibre products at Mentor Graphics in Cairo, Egypt.