These days, as I troll the pages of the Internet in search of juicy tidbits of 3D IC news and information, I’ve realized that with the exception of that pesky issue with thin wafer handling, focus has moved away from novel manufacturing processes, and turned its magnifying glass onto the world of design, test, reliability, signal and power integrity, ESD challenges, and so forth. This is proving to be a bit of a challenge for me, as designer engineers speak a whole different language than process engineers! In any case, despite what you may hear on the conference circuit about remaining roadblocks, progress IS being made (especially from the looks of new product releases).

At the top of the heap is Cadence, who claims to be the ONLY EDA vendor who has 8 test chips and one production chip in the market today. Here’s a video interview with Samta Bansal, product marketing manager, Cadence, that gives some more highlights of the company’s approach to 3D ICs.

And then back in June, Mentor Graphics made two announcements regarding the company’s readiness in the 2.5D and 3D IC space. The first was about the inclusion of Mentor system and IC design and implementation for TSMC’s Reference Flow 12 targeting its 28nm process technology, including 3DIC verification and test systems in Mentors Callibre and Tessant platforms. The second was the announcement of Mentor’s participation in both Tezzaron and MOSIS’ multi project wafer (MPW) programs, thereby providing a means for participating companies to test out 3D-IC concepts using the same provider and model they currently use for their standard semiconductors.

Another area said to be lacking is in the area of 3D test equipment, and I’ve heard people comment that Advantest and Teredyne really need to get with the program and come up with something. Well, it looks like Advantest has, with its June introduction of a concept model test cell dubbed, DIMENSION, which reportedly integrates a high parallel test cluster along with singulated die and 3D die stack automated handling capabilities to address thin die handling, test, and production line integration. The company introduced the concept at its Expo 2012, in Tokyo. Here’s the full press release.

Also in the test area is Multitest. And while the company doen’t build the test systems themselves, they do provide handling systems and claim to be ready to handle partial stacks for in-process tests. They recently presented at Test Vision 2012. If you missed it, you can access the presentation here. (They do require registration for the download).

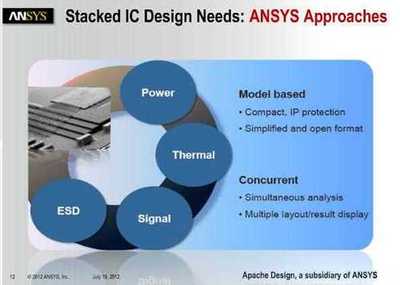

And just today, I tuned into a webcast today that was originally broadcast on July 26, and archived here. It’s a 30-minute promotional bit for Ansys Apache’s latest generation of its RedHawk design simulation platform that has reportedly been improved to enhance user experience, and was designed specifically to suit the needs of the 3D IC analysis environment.

Presenter Karan Sahni, a Senior Applications Engineer at Apache Design, Inc, explains that with 2.5D interposer and 3DIC designs using through silicon vias (TSVs), the need for reliability is “persistent.” He said technology trends are impacting power and noise, as higher switching currents lead to higher inductive noise. With a reduced noise margin, Sahni says you can experience functionality failures and over-design requirements. Redhawk 3DX enables low power analysis to get to the root cause of these issues in 3D ICs. If you are an IC designer using 3D/2.5D IC architecture, and have 30 minutes to spare, you should catch the webcast.

And speaking of the secret language used by the design community, here’s what appears to be an interesting round table discussion on the System-Level Design Community, moderated by Ed Sperling, on how to bring software in line with hardware to improve coherency (see what I mean?). Here’s what I understood after reading the dialogue (several times): Improved coherence equals improved performance. Co-design of software and hardware can help, but it mostly falls on how the software is written and how to share that information with the processor, or more accurately, between the CPU and GPU. SoCs are not the right model to deal with coherency. Subsystems drive the need for coherency because memories need to be cached, which is a drain on the CPU. When 2.5D and 3D comes into the mix, we’re might be dealing with level-3 cache. “Stacking in 3D could have an impact on this architecture, particularly on memory with Wide I/O. But 3D stacks also may complicate our lives because we have more choices, impacting the hardware architecture.

That’s all for now – think I’ll tackle an easier topic to report on tomorrow! ~ F.v.T.