I just finished putting together a presentation for the upcoming BiTS Workshop March 7-10, 2010 taking place in my backyard in Mesa, AZ. (Ok, it’s at the Hilton Phoenix East in Mesa – almost my back yard.) Here’s a bit of irony; my first visit (ever) to Arizona was due to the BiTS Workshop in 2007. To save our company travel expenses and because it was more fun, Gail Flower, then editor-in-chief of Advanced Packaging, and I accepted Leo’s generous offer to stay with his family. Since Leo and I are now business partners in 3D InCites, you could say it all got started thanks to BiTS Workshop. Funny how life happens.

So naturally, when Fred Taber, BiTS organizer, approached me in November about speaking at the event, I immediately accepted. However, I was a bit surprised, because when I think of BiTS (which stands for Burn-in Test Sockets Workshop) I think of board-level test, and the current issues around 3D ICs seem to be mostly wafer-level test issues. But then I remembered that the 3D paradigm changes everything, and the whole test community, from the wafer to the board, needs to tune into what’s going on in 3D integration so that they can be prepared for what’s coming.

Now I have to admit, test is not my strong suit, so I had to brush up on my knowledge and do some research. Coincidentally, I got an email from Bob Greenfield, who represents ASSET InterTech, a company that specializes in embedded instrumentation, asking me if I’d be interested in interviewing the company CTO, Al Crouch, who also happens to be a senior member of IEEE. The result of that exchange was the Test Forum discussion, On The Road to Resolving Test Issues for 3D Chip Stacks.

So with my information-on-test radar fully engaged, I paid close attention to those portions of the presentations at last month’s RTI 3D conference. Here’s some of what I learned:

From Jan Vardaman: on the issue of Known Good Die (KDG): Intel says “pretty good die” or “good enough die” will do, thanks to redundancy and built in self test (BIST). Test methodologies are still needed. Probe card issues – such as whether they are needed, companies that manufacture their own (TSMC, IBM) and non-contact approaches being investigated. “Potential users are interested in non-contact methods such as inductive, capacitive, and optical,” notes Vardaman.

From Bob Patti: Tezzaron’s BiSTAR (built in self test and repair) provides a solution thusly: it improves yield of highly parallel structures such as memory by virtue of integration of intelligent self test, self repair. It performs greater level of testing than normally available during normal chip or wafer level testing. Bi-STAR™tests and compares >300,000 nodes or bits/clock cycle; reportedly more than 1,000 times faster than can be achieved by any external memory tester.

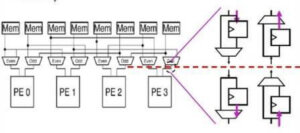

From Paul Franzon: With regard to KDG, Ignore yield, or get probably good die/wafers through test before integration. On probing: probing doesn’t scale. Better to test through special test interface, and rely on clean partitioning, self-test and scan to test to edge of each die. Finally, Use iJTAG to permit testing TO the TSV interface before assembly (see figure below).

From Phil Garrou: There’s very little information available on test. One question is whether to test every strata or only the full stack. However, he notes the test community is now aware, quoting a speaker at the 40th IEEE Test Conference in Austin as saying “…this year if I had to pick one theme it would probably be 3D” He also noted that the design and test communities are starting to work together, and referred attendees to a paper by Erik Jan Marinissen of IMEC on the topic.

(Note to self, ask Erik about this during our online discussion later next month).

And finally, today’s announcement of Cascade Microtech’s acquisition of SUSS MicroTec’s test division, and the subsequent collaborative agreement to develop measurement and test solutions for 3D TSV shows that at least two major suppliers are taking up the gauntlet.

As I said, the presentation has been submitted, but we all know that up-to-the-minute information is always welcome. So if anyone has anything to add, please let me know. I have 5 weeks left to prepare, so send me what you’ve got (or better yet, post it here so everyone can benefit from your knowledge!) –F.v.T.