It’s been a nearly a month since the 2017 IMAPS Device Packaging Conference and Global Business Council, so I’ve had plenty of time to mull over the many presentations and conversations focused on advanced packaging trends. The winds of change are blowing ever so slightly from year’s past. You had to listen carefully, and in some cases, read between the lines so not to miss them. I could report verbatim from the notes I gathered and the conference proceedings that I’ve had the opportunity now to review, but I’m not. Instead, I’m going to focus on the subtleties that can be detected only by those, like me, return year after year to listen to similar, yet different presentations that deliver new data as processes grow from R&D through commercialization, to optimization for high volume manufacturing.

It’s Not All About Mobile Anymore

The first few slides of almost every presentation talk about market drivers and industry trends. Suffice it to say that while smartphone and communications still represent the lion’s share of what’s driving advanced packaging technologies, growth is slowing, while it is increasing in automotive, internet of things (IoT), industrial, medical, and high-performance computing (servers).

Featuring Fan-out Anything

I remember the days when the 3D tracks were a sold-out show at the annual IMAPS Device Packaging conference. Not so this year! Fan-out packaging topics drew the biggest crowds, so much so that it was suggested they swap rooms when sessions filled to overflowing.

The fan-out inspired alphabet soup is growing. It’s not simply about fan-out wafer level packaging (FOWLP). We now have FoSiP, FoCoS, FoPoP, FoPLP, joining the branded line-up of eWLB, SLIM, SWIFT, InFO, and EMIB. (I will leave the task of deciphering those to you, Reader. It might make a good party game.) Suffice it to say that all the OSATS, foundries and IDMS are tossing their hat in the ring now that we know Apple likes FOWLP.

Picking up the Pace

The party line from OSATS regarding adopting new technologies has always been, “if it ain’t broke, don’t fix it.” According to Ron Huemoeller, Amkor, that’s not going to get us anywhere anymore. In his keynote about heterogeneous integration, he advised: “Technology is moving faster than it used to. You need to be in the forefront and have all your partners on board, need to have multi-source, not a single source.”

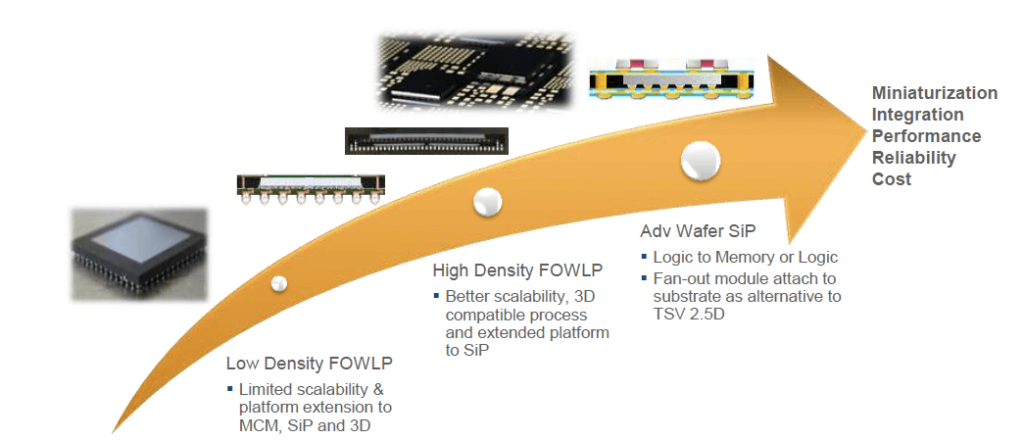

Hueomoeller, the man I once quoted as saying “once a package has been qualified and designed in, it’s here to stay”, has amended that viewpoint slightly, noting that while advanced packaging technologies are still numerous, the future of heterogeneous integration (simply put: die integration) boils down to three package platforms based on system architecture requirements: MEMS, laminate based advanced system-in-package (SiP), and wafer-based advanced SiP. The latter two are evolving out of fan-out wafer level packaging (FOWLP), as noted in Figure 1. Wafer-based advanced SiP offers an alternative to 2.5D through-silicon via (TSV) interposer technology. The main difference between the two? No TSVs.

According to Jérôme Azémar, Yole Développement, the FO market has reached a turning point. While there has been a solid ramp up of the technology and expectations for a promising core market, with lots of potential for high-density FO, he cautions about the possibility of “a fan-out bubble” because while it’s currently the hottest trend, in reality, the rapid growth in 2016 is associated with single product: TSMC’s InFO inside the Apple A10. Will this be a one hit wonder or will Apple competitors follow suit? Despite this risky scenario, Azémar sees growth potential in many markets including telecom, medical, industrial, automotive and more.

The Great Debate

Will fan-out panel level packaging (FOPLP) happen or not? We’ve been batting that one back and forth over the net for about a year now. The experts still don’t completely agree (in this case, the experts are Huemoeller, Phil Garrou, Rich Rice (ASE), Tom Strothman, (Kulicke & Soffa), Elvino Da Silveira (Rudolph Technologies) and Brandon Prior (Prismark Partners) – I’m sure there are more).

Going back to Huemoeller’s ‘single source’ theory – currently, there are not multiple tools and material supplier sources for FOPLP, and while he said some companies (mostly substrate suppliers) already support low-density FOPLP in low volumes, there’s concern that low-density FO won’t reach the volumes to require the volumes necessary to realize cost benefits of going to panel format. And as Phil Garrou pointed out, until the equipment suppliers can deliver tools for accommodating high-density fan-out, it will not happen.

Strothman concurs. “While there will be a time and place for FOPLP, it’s a bit risky for the equipment suppliers. eWLB lends itself to FOPLP because it is a large-format, low-density FOWLP. For high-density advanced fan-out technologies, it’s clear the path forward is in round format,” he said.

Rudolph is one supplier that’s taking the risk because they can leverage their platforms across both the advanced packaging and flat panel display markets. Silveira reported cost-of-ownership savings on lithography processes of 30-50% per die due to several reasons (Figure 2). Panels do not lose exposure areas, as is the case with round wafers, resulting in more die per panel and therefore a lower cost per package. According to Silveira, the company offers a high-volume lithography wafer platform that can process panels with <2µm RDL. However, according to Prismark Partners’ Brandon Prior, neither Rudolph nor other imaging equipment suppliers who have developed panel platforms, (ORC and Ushio) have shipped any tools.

According to Prior, to date there are a number of companies interested in and pursuing panel level approaches including STATS ChipPAC/JCET, Deca Technologies, ASE, PTI, SEMCO and In my coverage of the Fan-out Breakout Panel, I noted that according to Rice, ASE invested heavily in Deca Technologies to expand its panel line for WLCSPs and M-Series, its FOWLP offering because “It’s a viable technology and Deca has some pretty good ideas.”

3D TSVS will Enable the Future

At the end of the day, there comes a point in density requirements where FOWLP just won’t cut it. As Santosh Kumar, Yole Développement explained, a Si interposer is the best substrate for high-performance niche applications where design rules <1/1µm l/s are required.

According to Kumar, TSVs are now mainstream in high-performance applications (memory, FPGAs, high-end GPUs) thanks to companies like SK Hynix, Samsung, Tezzaron, Micron, Xilinx, AMD, and nVidia, and are on the heterogeneous integration roadmap. Yole predicts the total revenue of TSV applications to reach $7.2B by 2021 at a CAGR of 21%. While much of that growth continues to be in the MEMS and sensors space, dominated by CMOS image sensors (CIS), inroads are being made in logic and memory interposer integration by AMD, Nvidia, Cisco, Juniper, Huawei, Xilinx, HiSilicon, and IBM. TSVs will also be critical to emerging applications such as Si photonics and high-brightness LEDs.

So what will drive next-generation 3D technologies forward? Not smartphones. As Lionel Rudant, CEA-Leti put it, they are now a commodity. It will be “innovations of the hippest” – 5G, artificial intelligence, robotics, augmented reality – that provide new motivations for technology.

I know, I know. The more things change, the more they stay the same. But this time, it’s not about when 3D will arrive. It’s here. We’re just preparing for the next big wave. ~ F.v.T.